### Feature

- Support USB type-C protocol

-Configure as DFP (source)

-Broadcast 3A /1.5A current

- Support USB power delivery (PD) 2.0 and 3.0 and PPS protocol ---Integrated PD layered

- communication protocol

-PDO configurable: 5V, 9V, 12V, 15V,

-Apdo configurable: 5V prog, 9V prog,

- Support quick charge 3.0 /2.0 protocol -Configurable Xiaomi 27W charge Turbo

- Support Huawei FCP / SCP protocol

- Support Samsung AFC protocol

- Support USB BC1.2 DCP

- Support apple 2.4A charging

- Specification

- Integrated constant voltage (CV) compensation loop Integrated VBUS channel low impedance power switch

- built in VBUS discharge function

- Support line loss compensation function

- Support USB type

- -A and type-C dual port operation mode

- fast charging when port A or port C works independently

- when the A port is connected to the apple charging cable but not connected to the apple mobile phone, the C port still has fast charging

- when there are equipment access to port A and port C at the same time, it works at 5V

- Safety

- the type-A port is controlled by the switch at the power end to avoid the leakage caused by the short circuit

- overvoltage / undervoltage protection

- over current protection

- -Over temperature protection

- CC1 / CC2 / DP / DM overvoltage protection

- ESD characteristics ± 4KV

- Package: TSSOP-20

## Application

- AC-DC adapter

- USB Adapter

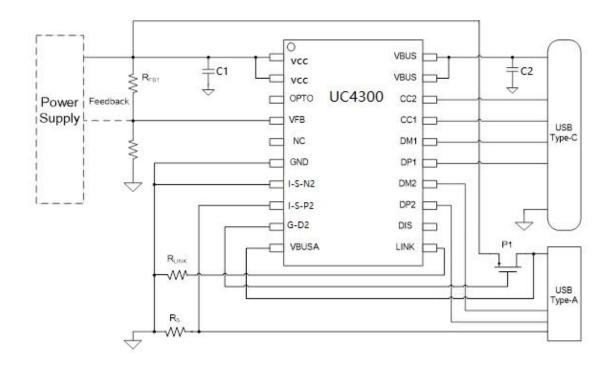

# **Application Circuit**

### DESCRIPTION

UC4300 is A multi-functional USB dual port controller integrating USB type-C, USB power delivery (PD) 2.0/3.0 and PPS, qc3.0/2.0 class B fast charging protocol, Huawei FCP / SCP fast charging protocol, Samsung AFC fast charging protocol, BC1.2 DCP and Apple device 2.4A charging specification, Provide complete type-C and type-a dual port charging solutions for AC-DC adapter, mobile power supply, car charger and other equipment.

UC4300 is specially integrated with plus PD-link Gamma Internet patent technology. Through plus PD-link Gamma With the interconnection function, UC4300 can be easily and flexibly applied in the charging scheme of multiple type-C and type-a ports.

The built-in type-C protocol of UC4300 can support the type-C device to be inserted into the Automatic wake-up system, identify the plug forward and reverse, and realize the connection. The integrated type-C pd3.0 protocol supports bi-directional mark coding (BMC), integrates the physical layer protocol and protocol engine of hardware, and does not need software to participate in encoding and decoding.

When one of the type-C and type-a ports is connected to the device, the type-C or type-A port can realize independent fast charging function. When both type-C and type-A are connected to the device, UC4300 will reduce the output voltage to 5V to supply power to the device. In particular, when the type-A port is always connected to the apple charging cable but not connected to the Apple phone, the type-C port still has the fast charging function. When used as A charger, the charging line is often connected to the charger. UC4300 perfectly solves the problem of fast charging when type-A and type-C port are connected with charging line. UC4300 built in A variety of protection mechanisms to ensure the safety of the equipment: including dynamic overvoltage / under voltage / overcurrent protection (the protection point can be adjusted according to the proportion of the working voltage / current requested by the equipment); start monitoring (the port voltage will be monitored before VBUS output). UC4300 integrates  $25m \Omega$  VBUS channel power switch and internal discharge channel, which saves peripheral devices and can quickly turn off output and restore to safe state in case of error.

UC4300 is packaged in TSSOP20.

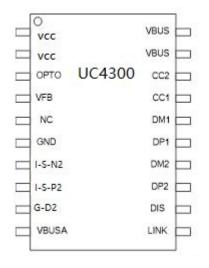

# **Pin function**

| PIN | NAME   | Description                              |

|-----|--------|------------------------------------------|

| 1/2 | VCC    | Source INPUT                             |

| 3   | ОРТО   | OPTO coupler driver                      |

| 4   | VFB    | Voltage adjust feedback connection       |

| 5   | NC     | No connection                            |

| 6   | GND    | GND                                      |

| 7   | I-S-N2 | Type-A port, current sense negative port |

| 8   | I-S-P2 | Type-A port, current sense positive port |

| 9   | G-D2   | Type-A port, PMOS Switch driver          |

| 10  | VBUS-A | Type-A port, output VCC                  |

| 11  | LINK   | Plus PD-LINK™ Port                       |

| 12  | DIS    | Control the discharge MOS gate           |

| 13  | DP2    | Type-A Port DP                           |

| 14  | DM2    | Type-A Port DM                           |

| 15  | DP1    | Type-C Port DP                           |

| 16  | DM1    | Type-C Port DM                           |

| 17  | CC1    | Type-C Port CC1                          |

| 18  | CC2    | Type-C Port CC2                          |

| 19  | VBUS   | VBUS output                              |

| 20  | VBUS   | VBUS output                              |

# **Order Information**

| name   | PDO And APDO Configuration                                          | mark   | package |

|--------|---------------------------------------------------------------------|--------|---------|

| UC4300 | High power OutputPDO : 5V/3A, 9V/3A, 12V/2.25A, 9V/2.2A (Apple 20W) | UC4300 | TSSOP20 |

| 004300 | Low power output PDO : 5V/2A                                        | 0C4300 | 1550F20 |

Mark information:

Line 1, UC4300: Chip mark;

Line 2, XXXXX: Lot Number;

## Available function

|        | QC3.0 | FCP/SCP | AFC | PD3.0 | PPS | A+C | Plus PD-link |

|--------|-------|---------|-----|-------|-----|-----|--------------|

| UC4300 | Y     | Y       | Y   | Y     | Y   | Y   | Y            |

## Specifications

### **Absolute Maximum Ratings**

|                                         | Min                                  | Max  | Unit |    |

|-----------------------------------------|--------------------------------------|------|------|----|

| Dualizar Vialta as (VS to CND)          | VIN, VCC, PS, CC, VBUS, OPTO, DP, DM | -0.3 | 24   | V  |

| Broken Voltage(VS to GND)               | The others Pin                       | -0.3 | 6    | V  |

| Operating Junction<br>Temperature Range |                                      | -40  | 150  | °C |

| Storage Temperature                     |                                      | -65  | 150  | °C |

(1) Absolute maximum ratings are stress limits beyond which damage to the device may happen..

### **ESD** feature

| Symbol           | Parameter | Value | Unit |

|------------------|-----------|-------|------|

| V <sub>ESD</sub> | HBM       | ±4000 | V    |

## **Recommended operating conditions**

|                   | Parameter                       |     | Туре | Max | Unit |

|-------------------|---------------------------------|-----|------|-----|------|

| VCC               | Input voltage                   | 3.6 |      | 15  | V    |

| C <sub>VBUS</sub> | Discharge limitation resistor   | 2.2 |      | 10  | μF   |

| C <sub>VCC</sub>  | VAUX Capacitor                  | 4.7 | 10   |     | μF   |

| R <sub>FBUP</sub> | VBUS Capacitor                  |     | 100  |     | kΩ   |

| T <sub>A</sub>    | System voltage divider resistor | -40 |      | 85  | °C   |

### Package thermal Data

| Symbol             | Parameter                                                 | Value | Unit |

|--------------------|-----------------------------------------------------------|-------|------|

| $R_{	heta JA}$     | Max Junction-to-Ambient Thermal Resistance (1)            | 100   |      |

| $R_{\theta JCtop}$ | Max Junction-to-Case Thermal Resistance                   | 36    | °C/W |

| $R_{	heta JB}$     | Thermal resistance between junction and plate temperature | 45    |      |

## **ELECTRICAL CHARACTERISTICS**

(T<sub>J</sub>=25°C, 5V $\leq$ VCC $\leq$ 12V, unless otherwise specified)

| Parameter             |                                       | Test conditions                                | MIN  | ТҮР   | MAX | UNI |

|-----------------------|---------------------------------------|------------------------------------------------|------|-------|-----|-----|

|                       |                                       | VCC, VBUS                                      |      | 1     | 1   |     |

|                       |                                       | Rising edge                                    |      | 3.3   |     |     |

| $V_{VCC\_TH}$         | VCC UVLO Threshold                    | Falling edge                                   |      | 2.9   |     | v   |

|                       |                                       | Hysteresis                                     |      | 0.4   |     |     |

| I <sub>SUPP</sub>     | Operating current                     | VCC=5V, VBUS=5V                                |      | 2     |     | mA  |

|                       | Vo                                    | ltage Protection (VBUS)                        |      |       |     |     |

| V <sub>FOVP</sub>     | Fast OVP Threshold, always<br>enabled | Ref to target voltage                          |      | +20%  |     | v   |

| V <sub>SOVP</sub>     | Slow OVP Threshold                    | Ref to target voltage                          |      | +15%  |     | V   |

| $V_{\text{SUVP}}$     | VBUS UVP Threshold                    | Ref to target voltage                          |      | -22%  |     | V   |

|                       |                                       | Switch MOSFET                                  |      | 1     |     |     |

| R <sub>DSON</sub>     |                                       |                                                |      | 25    |     | mΩ  |

|                       | Т                                     | ransmitter (CC1, CC2)                          |      |       | 1   |     |

| R <sub>TX</sub>       | Output resistance                     | During transmission                            |      | 50    |     | Ω   |

| V <sub>TXHI</sub>     | Transmit HIGH                         |                                                |      | 1.15  |     | V   |

| V <sub>TXLO</sub>     | Transmit LOW                          |                                                | -75  |       | 75  | mV  |

| tui                   | Bit unit interval                     |                                                |      | 3.3   |     | us  |

| t <sub>BMC</sub>      | Rise/fall time of BMC                 | R <sub>load</sub> =5.1k,C <sub>load</sub> =1nF | 300  |       | 600 | ns  |

|                       |                                       | Receiver (CC1, CC2)                            |      |       |     |     |

| V <sub>RXHI</sub>     | Receive HIGH                          |                                                | 800  | 840   | 885 |     |

| V <sub>RXLO</sub>     | Receive LOW                           |                                                | 485  | 525   | 570 | mV  |

| _                     | CC1/CC2 Broadcasting                  | 3A DFP mode, $0 \le V_{CCX} \le 2.5V$          | 304  | 330   | 356 | uA  |

| $I_{RP\_SRC}$         | current                               | 1.5A DFP mode, 0<br>$\leq V_{CCX} \leq 1.5V$   | 166  | 180   | 194 | uA  |

|                       |                                       | OCP                                            |      | 1     | 1   | 1   |

|                       |                                       | Ref to Power Capability(pd)                    |      | +30%  |     | A   |

| VITRIP                |                                       | USB-A                                          |      |       |     | A   |

|                       |                                       | OTP (internal)                                 |      | 1     | I   | 1   |

| _                     |                                       | Temperature rising edge                        | 135  | 145   | 155 | °C  |

| $T_{J1}$              | Die temperature                       | Hysteresis                                     |      | 20    |     | °C  |

|                       | HV                                    | DCP interface (DP, DM)                         |      | ı     |     |     |

| V <sub>DAT(REF)</sub> | Data line detection voltage           |                                                | 0.25 | 0.325 | 0.4 | v   |

| Support Plu                  | s PD-LINK USB I                                                       | Double ports Cor         | troller |       |      |    |

|------------------------------|-----------------------------------------------------------------------|--------------------------|---------|-------|------|----|

| V <sub>SEL(REF)</sub>        | Output voltage selection                                              |                          | 1.8     | 2     | 2.2  | V  |

| T <sub>GLITCH</sub> (DP)HIGH | D+ High level disturbance<br>filtering time                           |                          | 1       | 1.25  | 1.5  | s  |

| T <sub>GLITCH</sub> (DM)LOW  | D- Low level disturbance filtering time                               |                          |         | 1     |      | ms |

| T <sub>GLITCH(V)CHANGE</sub> | Output voltage disturbance filtering time                             |                          | 20      | 40    | 60   | ms |

| Tglitch(cont)change          | Disturbance filtering time in continuous mode                         |                          | 100     | 150   | 200  | us |

| R <sub>DAT(LKG)</sub>        | D+ Leakage resistance                                                 |                          | 300     | 500   | 800  | KΩ |

| R <sub>DM(DWN)</sub>         | D- DroPD-outputwn resistance                                          |                          | 14.25   | 19.53 | 24.5 | KΩ |

| R <sub>ON(N1)</sub>          | Switch N1 on resistance                                               |                          |         | 40    | 100  | Ω  |

| V <sub>TH(PD)</sub>          | Connection voltage<br>threshold of receiving<br>device                |                          | 0.25    | 0.325 | 0.4  | V  |

| $TD_{PD}$                    | Connection detection and<br>filtering time for receiving<br>equipment |                          | 120     | 160   | 200  | ms |

| $\Delta I_{T(UP)}$           | Step size of current source<br>when voltage rises                     | R <sub>IREF</sub> =100KΩ |         | 2     |      | uA |

| $\Delta I_{T(DO)}$           | Step size of current source when voltage is reduced                   | R <sub>IREF</sub> =100KΩ |         | 2     |      | uA |

|                              | Ар                                                                    | ple 2.4A Charge mode     |         | •     |      |    |

| V <sub>DAT(2.7V)</sub>       | D+/D- voltage                                                         |                          | 2.57    | 2.7   | 2.84 | V  |

| R <sub>DAT(2.7V)</sub>       | D+/D- output impedance                                                |                          |         | 15    |      | KΩ |

|                              |                                                                       | FCP charge mode          |         |       |      |    |

| VTX-VOH                      | D- FCP TX Valid High                                                  |                          |         | 2.7   |      | v  |

| V <sub>TX-VOL</sub>          | D- FCP TX Valid Low                                                   |                          |         |       | 0.3  | v  |

| V <sub>RX-VIH</sub>          | D- FCP RX Valid High                                                  |                          |         | 1.2   |      | v  |

| Vrx-vil                      | D- FCP RX Valid High                                                  |                          |         | 0.9   |      | v  |

| Trise                        | FCP Pulse Rise Time                                                   | 10% - 90%                |         |       | 2.5  | us |

| Tfall                        | FCP Pulse Fall Time                                                   | 90% - 10%                |         |       | 2.5  | us |

## **Application informatin**

### VCC 和 VBUS

VCC is the input power of type-C and type-a ports. It is used as the power input of VBUS and the power supply pin of the chip to connect the output of ACDC or DCDC. It is recommended to connect GND to  $2 \sim 10$ uF ceramic capacitor near VCC and VBUS pins.

### ОРТО

OPTO is used to Drive Optocoupler, with withstand voltage of more than 24V (see application diagram in Chapter 3).

### VFB

VFB and OPTO form CV loop, which needs to be compensated. The reference at VFB is 1.24v, and the partial voltage resistance near VCC must be 100k, and the other is 33K (corresponding to VCC = 5V); the resistance accuracy affects the power supply accuracy, so it is recommended to use 1% accuracy resistance.

#### Current Sense

UC4300 has two sets of current detection circuits, corresponding to port C and port A respectively. Port C current detection is completely built-in, and the default protection point is 130% of PDO current; port A current protection points are 2.8/3.2/3.6/4a optional (use 10m  $\Omega$  to detect resistance). The detection resistance of 10m  $\Omega$  needs to be connected by Kelvin, one end is ISP2, the other end is the GND of the chip.

#### Line loss compensation

UC4300 can increase the output voltage in proportion according to the load current (60 / 90 / 120 mV /A optional), and can also offset the output voltage in A fixed way (-  $150 \text{mV} \sim +400 \text{mV}$ ).

#### Multi-port Applications

UC4300 can realize fast charging in single port application, and it will return to 5V charging when A + C works at the same time; moreover, it can realize whether the apple cable or mobile phone is connected to port A through special technology to avoid affecting the quick charging of port C when there is only apple cable in port a.

#### Safety characteristics

#### Withstand voltage

In order to avoid chip damage caused by CC / DP / DM pin and power short circuit, the withstand voltage of these ports can reach more than 24V.

#### OVP/OCP/UVP

The chip OVP/OCP/UVP threshold will be adjusted according to the voltage selected by the device to protect the device security to the maximum extent.

#### OTP

When the chip junction temperature reaches 145 °C, the output will be closed, and when it drops to 125 °C, it will be released. $_{\circ}$

#### Discharge

UC4300 has built-in energy discharge channel, which can open the discharge power energy under specific circumstances  $_{\circ}$

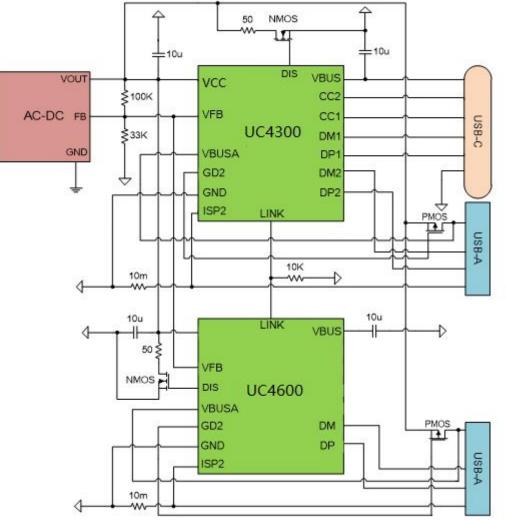

## 2A+1C application:

UC4300+UC4600: 2A+1C application

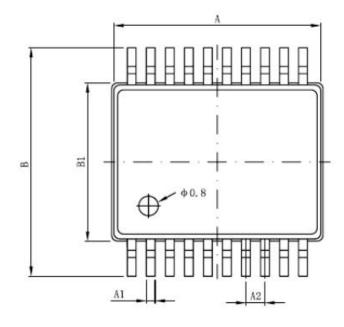

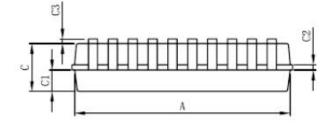

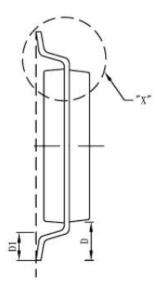

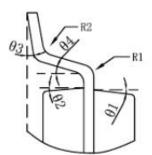

# **Package Information**

| 尺寸 | 最小(mm) | 最大(mm) | 尺寸 标注 | 最 小 (mm) | 最大(mm) |

|----|--------|--------|-------|----------|--------|

| A  | 6.40   | 6.60   | C3    | 0.05     | 0.15   |

| A1 | 0.20   | 0.30   | D     | 1.0T     | YP     |

| A2 | 0.65   | TYP    | D1    | 0.50     | 0.75   |

| В  | 6.30   | 6.50   | R1    | 0.15     | TYP    |

| B1 | 4.30   | 4.50   | R2    | 0.15     | TYP    |

| С  | 0.90   | 1.05   | θ1    | 12° 1    | TYP    |

| C1 | 0.4365 | TYP    | θ2    | 12° 1    | TYP    |

| C2 | 0.09   | 0.2    | 03    | 0° TYP   | 8° TYP |

|    |        |        | 04    | 10°      | TYP    |

DETAIL "X"